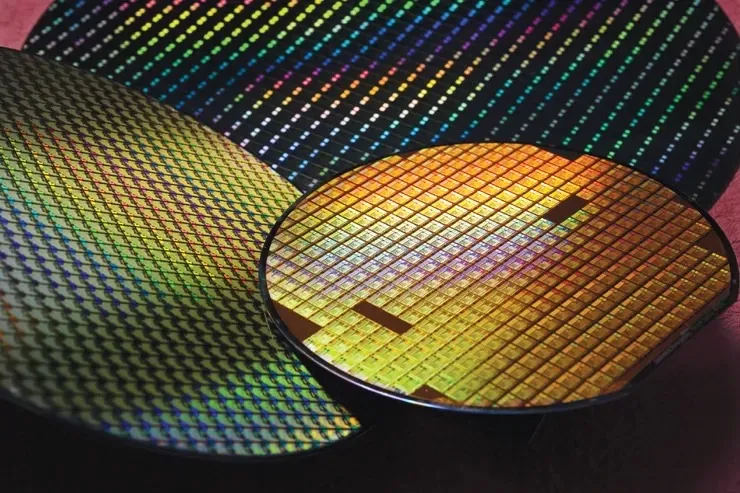

顾诗章回顾,自己使用Ansys已逾二十年,见证模拟工具的进步。他以AI晶片封装为例,说明3D IC透过中介层(Interposer)将运算晶片与记忆体晶片分拆制造后再高密度整合,甚至纳入光学元件、微流道冷却解决方案,让设计验证更为复杂。封装尺寸可达100×100毫米,但内部结构仅1微米等级,需同时处理材料、结构、电性与散热多面向参数,形成跨尺度运算挑战。

他指出,团队采取两大策略提升效率:其一,透过系统参数调校,在既有硬体与软体下效能提升26%;其二,利用开源排程工具优化资源分配,再进一步增效,最终整体效能提升约60%。顾诗章形容,这是工程师投入经验与心力后创造的附加价值。他并比较不同配置效益:采CPU+GPU组合虽能提升效能两倍,但成本增加三倍;若改用八倍CPU核心,效能可达5.6倍,成本仅为原来的两倍,性价比更佳。

Ansys台湾技术总监魏培森则是回应,GPU效能提升受限于任务拆分与资料回传,非线性倍增,若在6颗GPU已可带来45%至50%效能提升,仍具投资回报。Ansys将持续优化演算法并结合硬体架构改善,深化GPU加速技术,并依产业需求提供最佳化建议。

顾诗章表示,台积电将持续结合内部工程师调校经验与Ansys支援,推进3D IC与先进封装模拟效能,缩短开发周期并提升设计可靠度,期望客户满意度能从96.8%提升至99.99%,符合台积电一贯追求的高标准。

顾诗章也在与媒体交流时提到,台积电在先进封装的模拟验证工作大多自行执行,不会交由第三方代工,这不仅涉及知识产权与保密,更是效率的关键,并指出自己做能更快、更方便,不需要排队等外部资源,也能确保资讯安全。他直言,只有在内部完全没有相关资源的情况下,才会向外部设备厂寻求支援,但这属少数案例。

针对不同客户专案,他进一步指出,即使基础平台与规则相同,台积电仍建立严谨隔离机制,确保各专案独立运作,避免资料互相干扰或外泄,这样的模式能同时兼顾保密、速度与独立性,让台积电在开发过程中保持高度信任。

點擊閱讀下一則新聞

點擊閱讀下一則新聞