谢克指出,AI的竞争格局正在发生根本性转变,焦点不再局限於单颗晶片效能,而是涵盖自研加速器、资料中心网路、机架架构设计,到数据与开发平台,以及最终应用的「端到端AI基础设施」。他进一步将AI基础设施划分为三个层次:

第一是基础设施层,涵盖GPU/TPU等加速器、储存与资料中心网路。

第二是资料与开发层,包括数据平台、资料库与AI开发工具。

第三则是应用层,例如Google搜寻、YouTube、Android、Workspace与Gemini等服务。谢克强调,AI真正的价值不仅在于模型演进,更在于能否快速扩展至大规模使用者并解决实际问题。

在规模化挑战上,谢克透露,目前单一AI集群已可达9,000颗以上加速器,对互连架构提出极高要求,需要TB/s级频宽与极低延迟。由于任何元件失效都可能拖累整体效能,因此必须引入光学电路交换技术,确保系统具备可靠性与弹性重构能力。同时,能源效率问题亦成为大型资料中心不可回避的课题。

谢克也于论坛中展示Google光学互连技术的发展路线图,显示单通道传输速率自2018年的50G逐步提升,2024年已达200G,并预计2027年将推进至400G PAM4,模组整体频宽突破3.2Tbps。

谢克表示,光学互连将支撑AI丛集的「scale-up」与「scale-out」两大需求:前者负责超级计算集群(Pod)内部的高速低延迟沟通,后者则连结跨资料中心的长距离网路并提供更高冗余性,确保超大规模AI运算能持续扩展。

他进一步指出,AI算力需求的增速已经远超摩尔定律,传统电互连技术难以应付万卡等级丛集的挑战。矽光子技术因而成为未来的核心,包括矽光子收发器、共封装光学,以及资料中心级光交换,都是产业投资与合作的焦点。谢克直言,这是一场跨领域、跨供应链的合作竞赛,唯有晶片设计商、云端服务商与光电技术供应链共同投入,才能推动AI基础设施迈向下一世代。

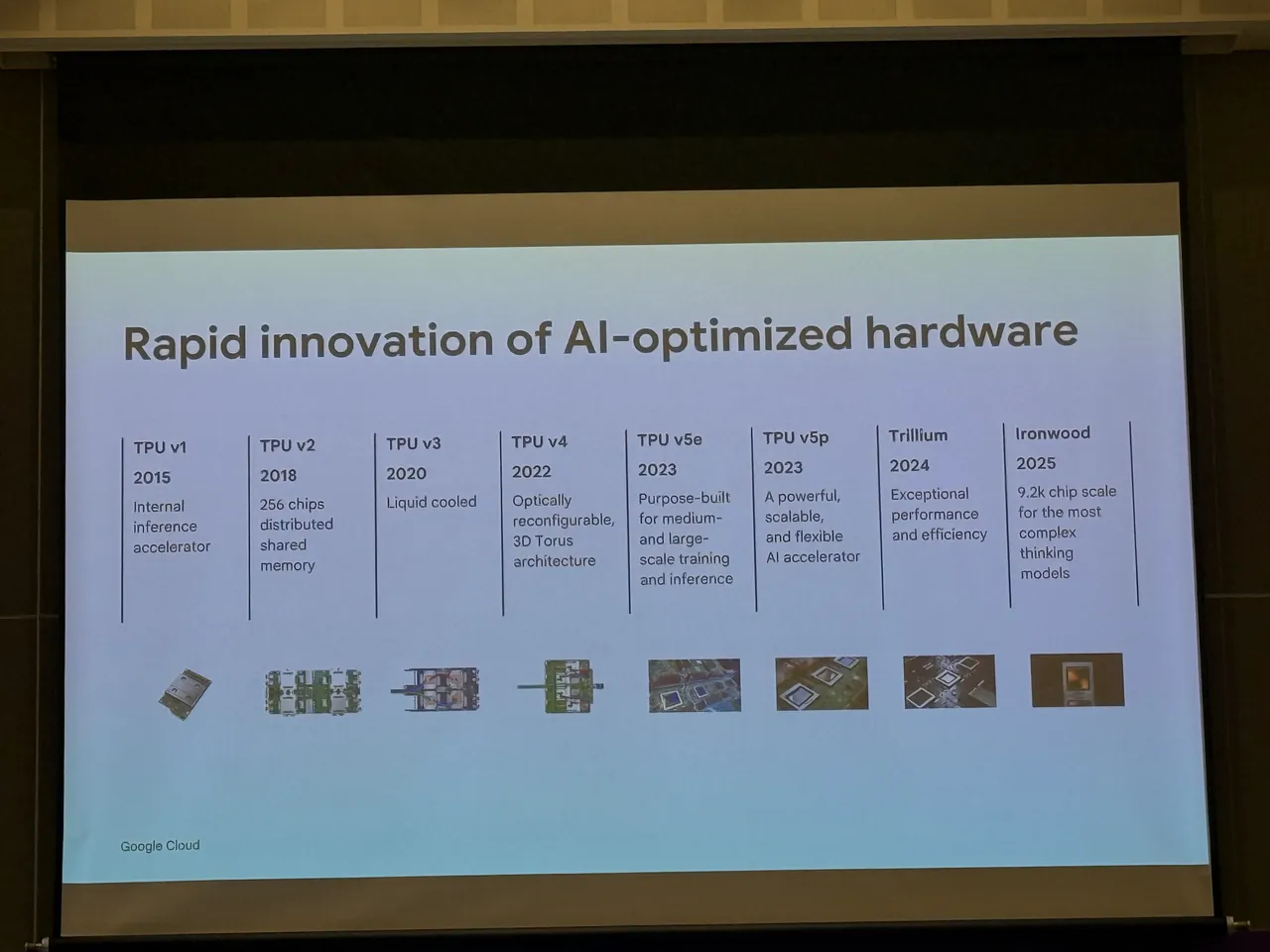

值得注意的是,Google同步揭示自研TPU的十年演进,展现AI专用晶片的快速迭代。自2015年TPU v1问世以来,陆续推出液冷的TPU v3、具光学可重构与3D Torus架构的TPU v4,以及支援中大型训练的TPU v5e与灵活扩展的TPU v5p。2024年则推出兼具效能与能效的Trillium,2025年预计发布Ironwood,单一集群规模将达9,200颗晶片,专为最复杂的AI思考型模型打造。这条TPU路线图正是谢克所言「端到端基础设施」理念的缩影,从晶片到丛集,逐步建构支撑全球级AI应用的完整生态。

點擊閱讀下一則新聞

點擊閱讀下一則新聞