科林研发推出VECTOR TEOS 3D 锁定AI与HPC先进封装应用

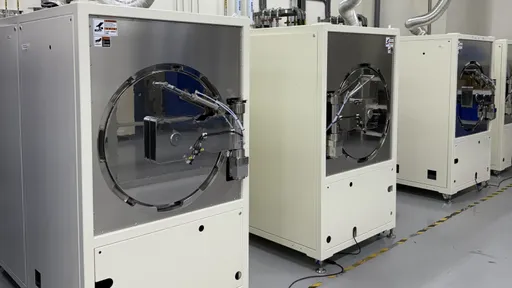

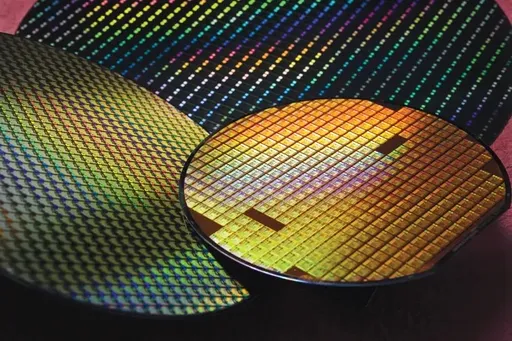

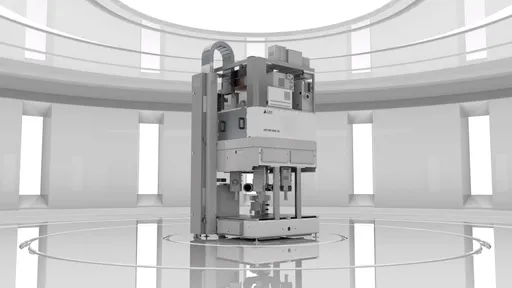

【记者吕承哲/台北报导】半导体设备大厂 Lam Research(科林研发)今(10)日正式发表全新沉积设备 VECTOR TEOS 3D,锁定次世代人工智慧(AI)及高效能运算(HPC)所需的先进封装应用。该设备聚焦于解决 3D 堆叠与高密度异质整合制程的关键难题,透过专有翘曲晶圆传送方案与介电沉积技术,实现超厚且均匀的晶片间介电层填充。搭配 Lam Research 的 Equipment Intelligence 技术,更能提升制程监控能力。目前 TEOS 3D 已在全球顶尖逻辑与记忆体晶圆厂投入使用,象征先进封装制程迈入新里程碑。